- 您现在的位置:买卖IC网 > Sheet目录1220 > IP-NCO (Altera)IP NCO COMPILER

�� �

�

�

�Chapter� 2:� Getting� Started�

�2–7�

�MegaWizard� Plug-In� Manager� Flow�

�Table� 2–1� describes� the� generated� files� and� other� files� that� may� be� in� your� project�

�directory.� The� names� and� types� of� files� specified� in� the� report� vary� based� on�

�whether� you� created� your� design� with� VHDL� or� Verilog� HDL.�

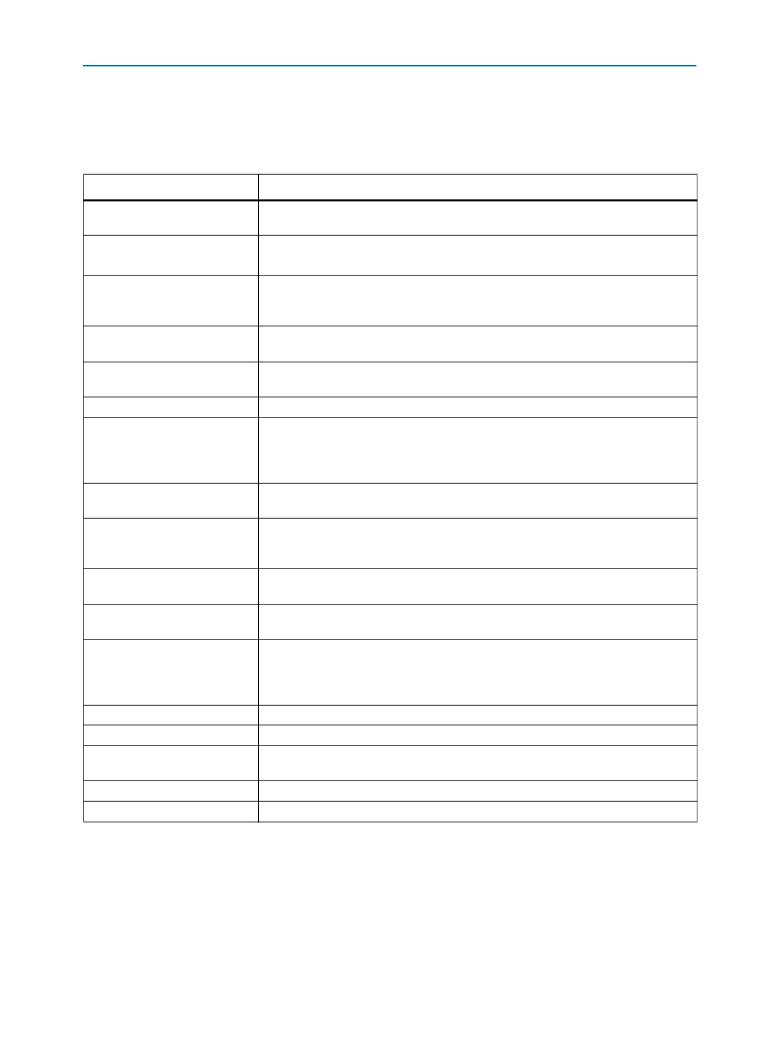

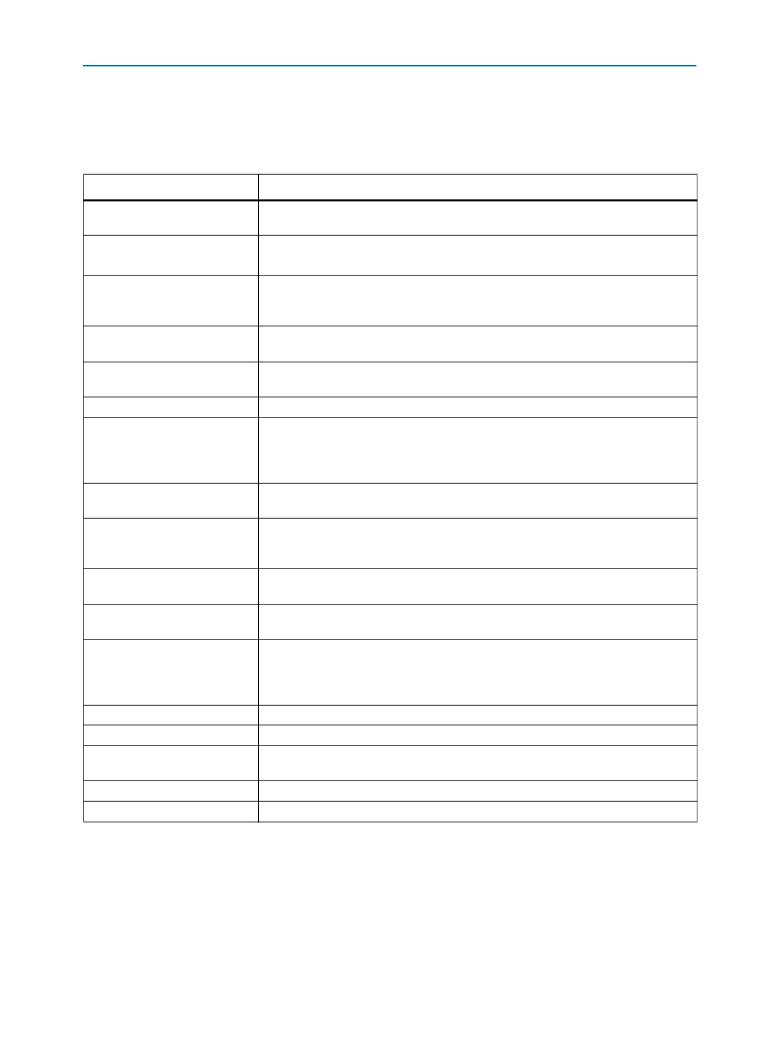

�Table� 2–1.� IP� Toolbench� Files�

�Filename� (1)� ,� (2)�

�<� entity� name� >.v�

�<� variation� name� >_vho_msim.tcl�

�<� variation� name� >_vo_msim.tcl�

�<� variation� name� >_tb.v� or�

�<� variation� name� >_tb.vhd�

�<� variation� name� >� .bsf�

�<� variation� name� >� .cmp�

�<� variation� name� >� .html�

�<� variation� name� >.qip�

�<� variation� name� >.vec�

�<� variation� name� >.vhd� or� .v�

�<� variation� name� >.vho� or�

�<� variation� name� >.vo�

�<� variation� name� >_bb.v�

�<� variation� name� >� _cos_c.hex,�

�<� variation� name� >� _cos_f.hex,�

�<� variation� name� >� _sin_c.hex,�

�<� variation� name� >� _sin_f.hex�

�<� variation� name� >� _syn.v�

�<� variation� name� >� _model.m�

�<� variation� name� >_nativelink.tcl�

�<� variation� name� >� _tb.m�

�<� variation� name� >_wave.do�

�Description�

�Generated� synthesizable� netlist.� This� file� is� required� for� Quartus� II� synthesis.� It� will� be�

�added� to� your� Quartus� II� project.�

�ModelSim� TCL� Script� that� runs� the� VHDL� or� Verilog� HDL� IP� functional� simulation� model�

�and� generated� VHDL� or� Verilog� testbench� in� the� ModelSim� simulation� software.�

�A� VHDL� or� Verilog� HDL� testbench� file� for� the� MegaCore� function� variation.� The� VHDL� file�

�is� generated� when� a� VHDL� top� level� has� been� chosen� or� the� Verilog� HDL� file� when� a�

�Verilog� HDL� top� level� has� been� chosen.�

�Quartus� II� symbol� file� for� the� MegaCore� function� variation.� You� can� use� this� file� in� the�

�Quartus� II� block� diagram� editor.�

�A� VHDL� component� declaration� file� for� the� MegaCore� function� variation.� Add� the�

�contents� of� this� file� to� any� VHDL� architecture� that� instantiates� the� MegaCore� function.�

�A� MegaCore� function� report� file� in� hypertext� markup� language� format.�

�A� single� Quartus� II� IP� file� is� generated� that� contains� all� of� the� assignments� and� other�

�information� required� to� process� your� MegaCore� function� variation� in� the� Quartus� II�

�compiler.� You� are� prompted� to� add� this� file� to� the� current� Quartus� II� project� when� you�

�exit� from� the� MegaWizard.�

�Quartus� II� vector� File.� This� file� provides� simulation� test� vectors� to� be� used� for� simulating�

�the� customized� NCO� MegaCore� function� variation� with� the� Quartus� II� software.�

�A� VHDL� or� Verilog� HDL� file� that� defines� a� VHDL� or� Verilog� HDL� top-level� description� of�

�the� custom� MegaCore� function� variation.� Instantiate� the� entity� defined� by� this� file� inside�

�of� your� design.� Include� this� file� when� compiling� your� design� in� the� Quartus� II� software.�

�A� VHDL� or� Verilog� HDL� output� file� that� defines� the� IP� functional� simulation� model.�

�Verilog� HDL� black-box� file� for� the� MegaCore� function� variation.� Use� this� file� when� using�

�a� third-party� EDA� tool� to� synthesize� your� design.�

�Memory� initialization� files� in� INTEL� Hex� format.� These� files� are� required� both� for�

�simulation� with� IP� functional� simulation� models� and� synthesis� using� the� Quartus� II�

�software.�

�A� timing� and� resource� estimation� netlist� for� use� in� some� third-party� synthesis� tools.�

�MATLAB� m-file� describing� a� MATLAB� bit-accurate� model.�

�A� Tcl� script� that� can� be� used� to� assign� NativeLink� simulation� testbench� settings� to� the�

�Quartus� II� project.�

�MATLAB� testbench� file.�

�ModelSim� Waveform� file.�

�Notes� to� Table� 2–1:�

�(1)� <� variation� name� >� is� a� prefix� variation� name� supplied� automatically� by� IP� Toolbench.�

�(2)� The� <� entity� name� >� prefix� is� added� automatically.� The� VHDL� code� for� each� MegaCore� instance� is� generated� dynamically� when� you� click� Finish�

�so� that� the� <� entity� name� >� is� different� for� every� instance.� It� is� generated� from� the� <� variation� name� >� by� appending� _st.�

�November� 2013�

�Altera� Corporation�

�NCO� MegaCore� Function�

�User� Guide�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IP-NIOS

IP NIOS II MEGACORE

IP-PCI/MT64

IP PCI 64BIT MASTER/TARGET

IP-PCIE/8

IP PCI EXPRESS, X8

IP-POSPHY4

IP POS-PHY L4

IP-RIOPHY

IP RAPID I/O

IP-RLDRAMII

IP RLDRAM II CONTROLLER

IP-RSDEC

IP REED-SOLOMON DECODER

IP-SDI

IP VIDEO INTERFACE - SDI

相关代理商/技术参数

IP-NIOS

功能描述:开发软件 Nios II MegaCore

RoHS:否 制造商:Atollic Inc. 产品:Compilers/Debuggers 用于:ARM7, ARM9, Cortex-A, Cortex-M, Cortex-R Processors

IPO-002-VSF-LF

制造商:PROXISTOR AB ELECTRONIC 功能描述:PROXIMITY SWITCH, PNP; Sensor Input:Inductive; Sensing Range Max:2mm; Supply Voltage DC Min:10V; Supply Voltage DC Max:30V; SVHC:No SVHC (19-Dec-2012); External Depth:10.5mm; External Length / Height:16.5mm; External Width:30mm;

IPOD TOUCH4-C-B

制造商:Distributed By MCM 功能描述:Apple® iPod Black Touch 4th Gen Digitizer + Glass 制造商:Distributed By MCM 功能描述:APPLE IPOD TOUCH DIGITIZER BLACK

IPOD TOUCH4-C-W

制造商:Distributed By MCM 功能描述:APPLE IPOD TOUCH DIGITIZER WHITE 制造商:Distributed By MCM 功能描述:Apple® iPod White Touch 4th Gen Digitizer + Glass

IPP015N04N G

功能描述:MOSFET OptiMOS 3 PWR TRANST 40V 120A RoHS:否 制造商:STMicroelectronics 晶体管极性:N-Channel 汲极/源极击穿电压:650 V 闸/源击穿电压:25 V 漏极连续电流:130 A 电阻汲极/源极 RDS(导通):0.014 Ohms 配置:Single 最大工作温度: 安装风格:Through Hole 封装 / 箱体:Max247 封装:Tube

IPP015N04NG

制造商:Infineon Technologies AG 功能描述:

IPP015N04NGHKSA1

制造商:Infineon Technologies AG 功能描述:Trans MOSFET N-CH 40V 120A 3-Pin(3+Tab) TO-220 制造商:Infineon Technologies AG 功能描述:N-KANAL POWER MOS - Rail/Tube

IPP015N04NGXKSA1

制造商:Infineon Technologies AG 功能描述:Trans MOSFET N-CH 40V 120A 3-Pin(3+Tab) TO-220 制造商:Infineon Technologies AG 功能描述:N-KANAL POWER MOS - Rail/Tube 制造商:Infineon Technologies AG 功能描述:MOSFET N-CH 40V 120A TO220-3